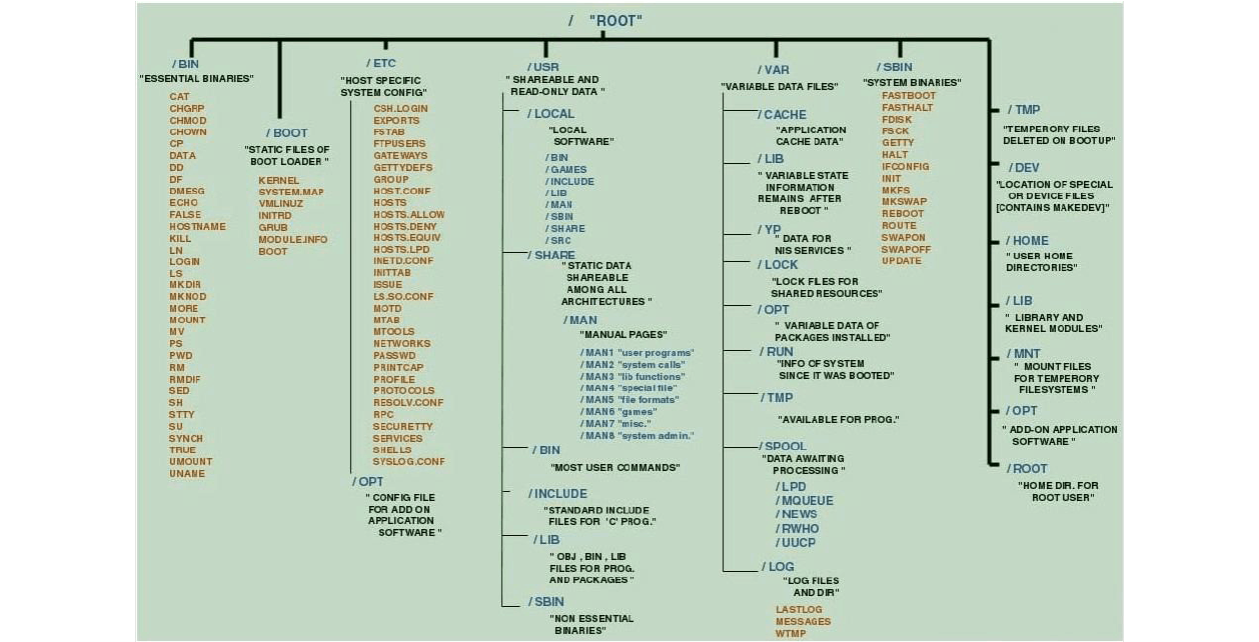

CPU简介

基本概念

CPU:( CentralProcessingUnit): 中央处理单元,CPU不等于物理核,更不等于逻辑核,一个逻辑核包含多个物理核,一个物理核可以分成n个逻辑核

物理核(physical core): 可以看的到的,真实的cpu核,有独立的电路元件以及L1,L2缓存,可以独立地执行指令。

逻辑核( logical core,LCPU): 在同一个物理核内,逻辑层面的核。1LCPU=1THREAD

超线程( Hyper-threading, HT):时间管理大师,超线程可以在一个逻辑核等待指令执行的间隔把时间片分配到另一个逻辑核。同一物理核超出的逻辑核之间为兄弟线程;

虚拟核:使用虚拟化技术,超分出的核心,位于虚拟机中;

CPU Die(裸晶): 生产中引入概念,从晶圆上切下来的裸晶,通过片外总线互联,可以封装在一个Package中,die之间通过HT(HyperTransport)总线通信

CPU Package(封装):对应一个cpu socket的一个CPU;

双路服务器:主板上有两个cpu插槽(socket),多个处理器通过 QPI 链路相连;

对称多处理机(Symmetric multiprocessing,SMP):每个处理器的地位都是平等的,对资源的使用权限相同。拥有超过一个以上的处理器,这些处理器都连接到同一个共享的主存上,并由单一操作系统来控制。在多核心处理器的例子中,对称多处理架构,将每一个核心都当成是独立的处理器。

下图为双路服务器的两个CPU,每个CPU 封装了4个die

cpu缓存

CPU高速缓存(cpu cache)目的是减少处理器访问内存的延时,在存储体系中仅次于cpu寄存器,速度快,接近处理器频率;

缓存是SRAM(Static Random Access Memory),使用CMOS(Complementary Metal-Oxide-Semiconductor)工艺;

基本原理

- 处理器访问内存时先检查cache中是否存在,命中则返回,未命中,存入cache再返回;

- 处理器写入内存时命中直接改写,未命中按照策略,写入或不写入cache;

缓存级别(常见)

缓存一般有三层,L1距离cpu最近,运行速率最高,容量最小;一般L1、L2为每个物理核独占

曾经有过L4 Cache 是个eDRAM,(Haswell/Broadwell:在Iris系列中)

缓存的设计

- exclusive:L1 cahce中的内容不能包含在L2中

- strictly inclusive:L1cache的内容一定严格包含在L2中。

- Third one(没有正式名字):不要求L1的一定包含在L2中

背景事件

晶体管的诞生

1947年贝尔实验室的肖克莱、布拉顿、巴丁共同发明晶体管(包括二极管、三极管、晶闸管、场效应管等),晶体管相比电子管功耗低、效率高。

八叛逆与仙童半导体

1955年,肖克利回到老家硅谷创建“肖克利半导体实验室”,两年招募8位年轻的科学家;后八人退出并找到Fairchild摄影器材公司的投资成立Fairchild仙童半导体。

Intel的成立

因仙童半导体与母公司矛盾,1968年7月,诺依斯和摩尔、格鲁夫脱离仙童成立Intel

AMD的成立

1969年5月,桑德斯带着7位仙童员工创办AMD

Intel 4004

1971年11月,英特尔公司推出了世界上第一款CPU Inter 4004,这是第一个可用于微型计算机的四位微处理器。此时MOS LSI(大规模集成)技术的可用性,刚刚开始在计算器业务从机电到电子的根本变化,4004的出现宣布了电子一体化的新时代,开始为PC机的出现铺路。

| 时钟频率 | 类型 | 晶体管 | 工艺 |

|---|---|---|---|

| 740kHz | 4bit 单核 | 2300 | 10微米 |

但当时的Inter作为一个小厂难以达到IBM 1620在1960的算力水平。

Inter在1972年生产了Inter 8008,打算用作终端控制器,与Inter 4040类似,是第一个8bit处理器

| 时钟频率 | 类型 | 晶体管 | 工艺 |

|---|---|---|---|

| 200-800KHz | 8bit单核 | 3500 | 10微米 |

TMS 1000

德州仪器(TI)生产,这是第一个包含足够RAM和足够用于程序ROM的空间以及在单个芯片上具有I / O支持的微处理器。从而使其无需多个芯片即可运行外部支持芯片,使其成为第一个微控制器。它还具有一项创新功能,可以向CPU添加自定义指令。

不足:内存不是连续的,内存都是内部的。所有硬连线都是单周期的,不允许中断。

Intel 8080

974年4月,8008的后续产品8080发布,是第一个成功的PC机Altair的处理器。

14位的PC和寻址功能,16位地址总线和8位数据总线,七个8位寄存器。

| 时钟频率 | 类型 | 晶体管 | 工艺 |

|---|---|---|---|

| 2MHz | 8bit单核 | 4500 | 6微米 |

有IO端口,可以连接256个IO设备。因此可以连接I / O设备而不会占用或干扰寻址空间,还有一个信号引脚,该信号引脚可使堆栈占用单独的内存

x86架构出现 Intel 8086

1978年6月Intel 8086发布,x86架构诞生

总线接口单元通过一个6字节的预取队列将指令流馈送到执行单元,因此,获取和执行是并发的-流水线的一种原始形式。

数据寄存器通常被指令隐式使用,使临时值的寄存器分配变得复杂。它具有64K 8位I / O(或32K 16位)端口和固定向量中断。还可以通过索引寄存器设置四个段寄存器

| 时钟频率 | 类型 | 晶体管 | 工艺 |

|---|---|---|---|

| 5MHz | 16bit单核 | 29000 | 3微米 |

不足:与大多数分段处理器一样,8086不仅提供缺失的字节,还将分段寄存器(X 16或左移4位)添加到地址中。由于不增加地址位的情况下扩展地址空间而进行尝试的奇怪结果,有可能使两个具有相同值的指针指向两个不同的存储位置,或者使两个具有不同值的指针指向同一位置,并且受到限制典型的数据结构小于64K。但在高级语言中却引起了持续的混乱(例如近/远指针)。更糟糕的是,这使得将地址空间扩展到1 MB以上变得困难。

Intel 80286(1982)

80286芯片,该芯片比8006和8088都有了飞跃的发展,时钟频率由最初的6MHz逐渐提高到20MHz。其内部和外部数据总线皆为16位,地址总线24位,可寻址16MB内存。采用PGA的正方形包装

| 时钟频率 | 类型 | 晶体管 | 工艺 |

|---|---|---|---|

| 6MHz | 16bit 单核 | 134000 | 1.5微米 |

从80286开始,CPU的工作方式也演变成两种:实模式和保护模式。

实模式:微处理器可以访问内存限制在1MB

保护模式:保护操作系统,遇到异常使用时系统不会停机

不足:仅通过添加新模式将设计扩展到32位。进行切换返回时需要使用原始80286中被保留了下来的bug进行切换。所有内存访问都仍然限于64K段。

Intel 80386(1985)

具有几种处理器模式(包括单独的分页和分段模式),添加了MMU,安全模式

英特尔为80386设计了高速缓存(Cache),采取预读内存的方法来缓解这个速度瓶颈,从此以后,Cache就和CPU成为了如影随形的东西。

英特尔借此机会修复了以前设计中剩余的一些最受欢迎的功能。转向x86-64,AMD决定进一步改进设计,增加了更简洁的64位模式

| 时钟频率 | 类型 | 晶体管 | 工艺 |

|---|---|---|---|

| 16MHz | 32bit 单核 | 275000 | 1.5微米 |

不足: 64位功能被设计为32位附加组件,并且在低端版本中被禁用。启用后,扩展的32位流水线将比主流水线晚1/2个时钟周期。

Intel 80486(1989)

将80386和数学协微处理器80387以及一个8KB的高速缓存集成在一个芯片内。

添加了完整的流水线,单片8K缓存,片上FPU和时钟加倍版本(例如Z-280)。

内部缓存缩短了微处理器与慢速DRAM的等待时间。

在80×86系列中首次采用了RISC(精简指令集)技术,可以在一个时钟周期内执行一条指令。它还采用了突发总线方式,大大提高了与内存的数据交换速度。

| 时钟频率 | 类型 | 晶体管 | 工艺 |

|---|---|---|---|

| 25MHz | 32bit 单核 | 1.2M | 1微米 |

不足:CPU的频率越来越快,而PC机外部设备受工艺限制,能够承受的工作频率有限,这就阻碍了CPU主频的进一步提高。

在486的基础上,发展出了Intel 80486 DX/SX/DX2/DX4/SL CPU;Inter486 OverDrive,TI 486Dx,Cyrix 486DLC,Cyrix5x86,AMD 5×86

微(micro)架构的出现

intel推出奔腾系列,P5微架构;

amd推出K5微架构竞争,性能较差;

Intel Pentium(1993)

它也是第一个超标量Intel x86处理器(Intel公司把这种同时执行两条指令的能力称为超标量技术)。它具有双Integer流水线和单个浮点单元,允许它每个时钟发出并完成多个指令。

从PENTIUM开始,我们大家有了超频这样一个用尝试少的钱换取尝试多的性能的好方法

从Pentium开始,CPU封装开始出现扇热盖的设计,CPU的发热问题已经突显。

| 时钟频率 | 类型 | 晶体管 | 工艺 |

|---|---|---|---|

| 60, 66MHz | 32bit 单核 | 3.1M | 0.8微米 |

不足:i586程序(这个程序还有一些其他的名字,比如Linux用户就把它称为f00f程序)是一种越界攻击手段,处理器芯片会因为无法执行这个程序发来的非法指令而出现死机现象。

这个程序似乎并没有利用奔腾CPU里浮点运算的弱点,它直接向CPU送去错误的指令。这种死机现象除了手动重置计算机外没有其他好的解决办法

Intel Pentium Pro(1995)

为工作站和服务器设计,超算ASCI Red(第一台达到每秒万亿次浮点运算的计算机)。

Pentium临的是在Pentium Pro的一个封装中除Pentium Pro芯片外还包括一个256KB的二级缓存芯片,两个芯片之间用高频宽的奔腾Pro200MHZ CPU的L2 CACHE即正在运行在200MHZ上,内部通讯总线互连,处理器与高速缓存的连接线路也被安置在该封装中,这样就使高速缓存能更容易地运行在更高的频率上。

| 时钟频率 | 类型 | 晶体管 | 工艺 |

|---|---|---|---|

| 200MHz | 32bit 单核 | 5.5M | 0.35微米 |

不足:但是肇因于0.35微米制程发热功率甚大,故其时脉不曾高于233 MHz(正式版不能超频)。此外,由于指令队列的问题,Pentium Pro的16bit指令执行能力低于Pentium,造成Windows3.X和Windows9X与DOS系统下Pentium Pro性能低下。

64位处理器的诞生

- 1961年:IBM发表IBM 7030 Stretch 超级电脑。它使用64位资料字组,以及32或64位的指令字组。

- 1999年:Intel发布IA-64架构的指令集。AMD首次公开64位集以扩展给IA-32,称为x86-64(后来改名为AMD64)。

Intel Xeon(2001)

主要供非消费级服务站,服务器和嵌入式系统使用。

基于英特尔的NetBurst架构,有更高级的网络功能,及更复杂更的3D图形性能,另一方面,支持至强的芯片组也在并行运算、支持高性能I/O子系统(如SCSI磁盘阵列、千兆网络接口)、支持PCI总线分段等方面更好地支持服务器端的运算。

| 时钟频率 | 类型 | 晶体管 | 工艺 |

|---|---|---|---|

| 1.7GHz | 32bit 单核 | 42M | 180nm |

多核处理器的出现

2000年IBM发布POWER4,双核心处理器;

2005年4月,AMD发布皓龙(Opteron)双核处理器

Core 2(2009)

第一款微架构处理器,取代由2000年起大多数英特尔处理器采用的NetBurst架构。

提升缓冲存储器效率、核心数量等作出优化。这些新处理器的功耗比以往的Pentium 4/D处理器低很多。

| 时钟频率 | 类型 | 晶体管 | 工艺 |

|---|---|---|---|

| 1.06GHz~3.33GHz | 64bit,1,2,4核 | 291M | 65nm |

不足:Core 2处理器的主板售价较高,导致组装成本大幅增加所致

Alder Lake 大小核

待补充。。。